# Topics

- Communication theory

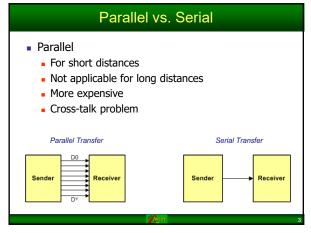

- Parallel vs. Serial

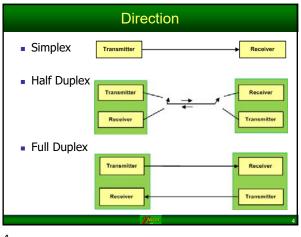

- Direction: Simplex, Half duplex, Full duplex

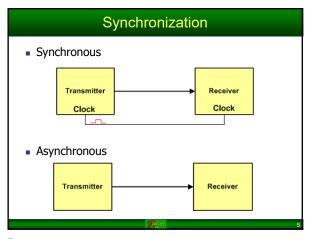

- Synchronization: Synchronous vs. Asynchronous

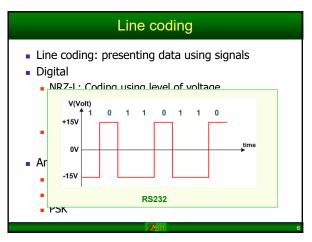

- Line coding

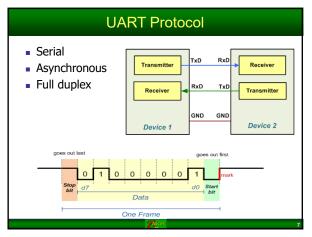

- UART protocol

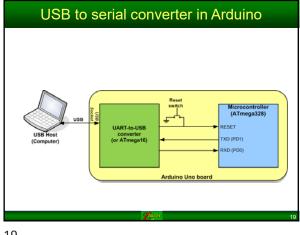

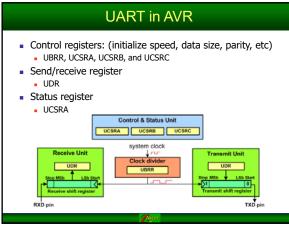

- UART in AVR

- UART Registers

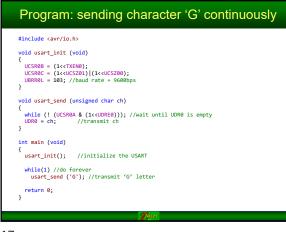

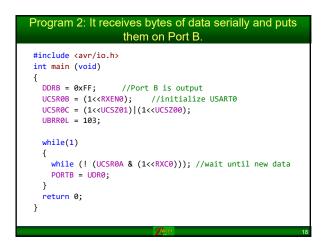

- Some programs

2

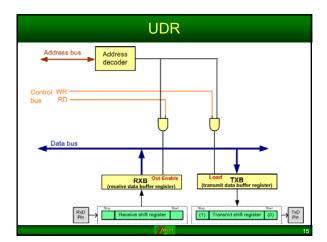

### USART (Universal Synchronous Asynchronous Receive Transmit)

- USART devices can be used to communicate asynchronously (UART) and synchronously.

- Since the synchronous capability of USART is not used nowadays, we concentrate on UART.

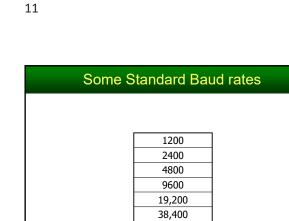

57,600 115,200

# **UCSRB**

### UCSRB: RXCIE0 TXCIE0 UDRIE0 RXEN0 TXEN0 UCSZ02 RXB80 TXB80

- RXCLE0 (Bit 7): Receive Complete Interrupt Enable

To enable the interrupt on the RXCn flag in UCSR0A you should set this bit to one.

TXCLE0 (Bit 5): USART Data Register Empty Interrupt Enable

To enable the interrupt on the RXCn flag in UCSR0A you should set this bit to one.

UDRIEO (Bit 5): USART Data Register Empty Interrupt Enable

To enable the interrupt on the UDRE0 flag in UCSR0A you should set this bit to one.

RXENO (Bit 4): Receive Enable

To enable the interrupt on the UDRE0 flag in UCSR0A you should set this bit to one.

RXENO (Bit 4): Receive Enable

To enable the USART receiver you should set this bit to one.

TEXENO (Bit 3): Transmit Enable

To enable the USART receiver you should set this bit to one.

UCSZ02 (Bit 3): Character Size

This bit combined with the UCS21:0 bits in UCSRC sets the number of data bits (character size) in a frame.

RXB80 (Bit 1): Receive data bit 8

This is the ninth data bit of the received character when using serial frames with nine data bits.

TXB80 (Bit 0): Transmit data bit 8

This is the ninth data bit of the transmitted character when using serial frames with nine data bits.

13

| UCSRC |                                                                       |                                                                                    |                                                               |                        |                 |             |             |        |            |

|-------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------|-----------------|-------------|-------------|--------|------------|

| ucs   | RC: UMSEL01                                                           | UMSEL00                                                                            | UPM01                                                         | UPM00                  | USBS            | 0 UCS       | SZ01 U      | ICSZ00 | UCPOLO     |

| •     | 00 = 4<br>01 = 5<br>10 = F<br>11 = F<br>UPM01:00 (Bit 1<br>These bits | select the oper<br>Asynchronous U<br>Synchronous US<br>Reserved<br>Master SPI (MSF | ration mode<br>SART operation<br>ART operation<br>PIM)<br>ode | of the USAR<br>on<br>1 |                 | ration and  | check.      |        |            |

|       | 01 = F                                                                | Reserved<br>Even Parity                                                            |                                                               |                        | 1               | UCSZ02      | UCSZ01      | UCSZ00 | Char. size |

|       |                                                                       | Odd Parity                                                                         |                                                               |                        |                 | 0           | 0           | 0      | 5-bit      |

| Ì     | USBS0 (Bit 3): 5                                                      | Stop Bit Selec                                                                     | t                                                             |                        |                 | 0           | 0           | 1      | 6-bit      |

|       | <ul> <li>This bit sel</li> <li>0 = 1</li> </ul>                       |                                                                                    | s the number of stop bits to b                                |                        | be transmitted. | 0           | 1           | 0      | 7-bit      |

|       | 1 = 2                                                                 |                                                                                    |                                                               |                        |                 | 0           | 1           | 1      | 8-bit      |

|       | UCSZ01:00 (Bit                                                        |                                                                                    | 1                                                             | 1                      | 1               | 9-bit       |             |        |            |

| 1     |                                                                       | combined with                                                                      |                                                               | bit in UCSR0           | B set the       | e character | size in a f | rame.  |            |

| ÷     | UCPOL0 (Bit 0):                                                       | Clock Polarit                                                                      |                                                               |                        |                 |             |             |        |            |

14

# **UCSRA**

#### UCSRA: RXC0 TXC0 UDRE0 FE0 DOR0 UPE0 U2X0 MPCM0

- RXC0 (Bit 7): USART Receive Complete 0

- RXC0 (Bit 7): USART Receive Complete 0

This flag bit set when there are new data in the receive buffer that are not read yet; It is cleared

TXC0Bit (Site) (

- DOR0 (Bit 3): Data OverRun 0 This bit is set if a data overrun is detected. A data overrun occurs when the receive data buffer and recover shift register are full, and a new start bit is detected. PE0 (Bit 2): Penty Error 0 That a party error when received. U2X0 (Bit 1): Double the USART Transmission Speed 0 MPCM0 (Bit 0): Multi-processor Communication Mode 0

16